|                                                           | 1 | /18 |

|-----------------------------------------------------------|---|-----|

|                                                           | 2 | /18 |

|                                                           | 3 | /16 |

| MASSACHUSETTS INSTITUTE OF TECHNOLOGY                     | 4 | /15 |

| DEPARTMENT OF ELECTRICAL ENGINEERING AND COMPUTER SCIENCE | 5 | /18 |

| 6.191 Computation Structures                              | 6 | /15 |

| Fall 2023                                                 |   |     |

## Quiz #1

| Name                    |                 | Athena logi | п пате   | Score                |

|-------------------------|-----------------|-------------|----------|----------------------|

| Solutions               |                 |             |          |                      |

| Recitation section      |                 |             |          |                      |

| ☐ WF 10, 34-301 (Wendy) | □ WF 2, 34-303  | (Jessica)   | □ WF 1   | 2, 36-155 (Joey)     |

| ☐ WF 11, 34-301 (Wendy) | □ WF 3, 34-303  | (Jessica)   | □ WF 1   | , 36-155 (Joey)      |

| ☐ WF 12, 35-310 (Rona)  | □ WF 10, 34-302 | 2 (Helen)   | □ WF 1   | , 34-303 (Catherine) |

| ☐ WF 1, 35-308 (Rona)   | □ WF 11, 36-112 | 2 (Helen)   | □ WF 2   | , 34-304 (Catherine) |

|                         |                 |             | ☐ opt-or | ut                   |

Please enter your name, Athena login name, and recitation section above. Enter your answers in the spaces provided below. Show your work for potential partial credit. You can use the extra white space and the back of each page for scratch work.

6.191 Fall 2023 - 1 of 19 - Quiz #1 Solutions

## **Problem 1. The Digital Abstraction (18 points)**

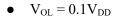

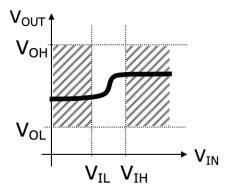

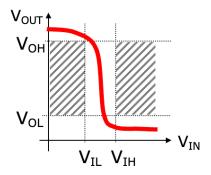

Device F has the following digital voltage thresholds and voltage transfer curve.

$$\bullet \quad V_{IL} = 0.2 V_{DD}$$

$$\bullet \quad V_{IH} = 4$$

$$\bullet \quad V_{OH} = 0.8 V_{DD}$$

- (A) (2 points) You are told that if  $V_{DD} = 1$  V ( $V_{OL} = 0.1$ V,  $V_{IL} = 0.2$ V,  $V_{IH} = 4$ V,  $V_{OH} = 0.8$ V), then F is invalid because it does not operate as a valid digital inverter with positive noise margins. Based on your understanding of the static discipline, provide **two** reasons to explain why this  $V_{DD}$  does not produce a valid inverter.

- 1) To be a valid specification,  $V_{OH}$  must be  $> V_{IH}$ , but 0.8 < 4. This would lead to negative noise immunity.

- 2) For a valid high input,  $V_{IH}$ , an inverter should produce a valid low output where  $V_{out} < V_{OL}$  but this circuit produces an output of 0.2 which is  $> V_{OL}$  so it is producing an output in the forbidden zone.

(B) (6 points) Now consider the following additional values of V<sub>DD</sub>. For each value, determine whether **F** is *valid* (i.e. it can function as a valid digital inverter with positive noise margins). If **YES**, then write the noise immunity for **F**. Otherwise, write **INVALID** and briefly explain your reasoning. Note that the thresholds for each value of V<sub>DD</sub> have been computed for you and are shown in parentheses.

i.  $V_{DD} = 4.5 \text{ V } (V_{OL} = 0.45 \text{ V}, V_{IL} = 0.9 \text{ V}, V_{IH} = 4 \text{ V}, V_{OH} = 3.6 \text{ V})$ Noise immunity or INVALID? \_\_\_\_\_ INVALID \_\_\_\_\_

Brief explanation:

Negative Noise immunity ( $V_{OH} = 3.6 < V_{IH} = 4$ )

ii.  $V_{DD} = 5.5 \text{ V } (V_{OL} = 0.55 \text{V}, V_{IL} = 1.1 \text{V}, V_{IH} = 4 \text{V}, V_{OH} = 4.4 \text{V})$ Noise immunity or INVALID? \_\_\_\_\_\_0.4 Brief explanation:

For all valid low inputs ( $V_{in} < 1.1$ ) this circuit produces an output of 4.5V which is a valid high output because it's  $> V_{OH}$  which is 4.4.

For all valid high inputs ( $V_{in} > 4$ ) this circuit produces an output of 0.2V which is a valid low output because it's  $< V_{OL}$  which is 0.55.

Noise immunity = min(4.4 - 4, 1.1 - 0.55) = min(0.4, 0.55) = 0.4

iii.  $V_{DD} = 6 V (V_{OL} = 0.6V, V_{IL} = 1.2V, V_{IH} = 4V, V_{OH} = 4.8V)$ Noise immunity or INVALID? \_\_\_\_\_ INVALID \_\_\_\_\_ Brief explanation:

For valid low inputs ( $V_{in} \le 1.2$ ) this circuit produces an output of 4.5V which is  $\le V_{OH}$  so it produces invalid outputs.

(C) (3 points) For what range of values for  $V_{DD}$ , if any, is  $\mathbf{F}$  valid (i.e., has noise immunity > 0)?

In order to have a positive high noise margin,  $V_{OH} = 0.8V_{DD}$  must be  $> V_{IH} = 4$ . This means that  $V_{DD} > 5$ .

At the other extreme, we want the output produced for valid low inputs to be >  $V_{OH}$ . Since the max output that our VTC can produce is 4.5V. It must be the case that  $4.5 > 0.8 V_{DD}$  so  $V_{DD} < 4.5/0.8 = 5.625$  or 45/8 = 5 and 5/8.

$5 \le V_{DD} \le 5.625$

You set F aside and move on to devices J and K. You find the following voltage thresholds for J and K.

$$\bullet V_{\rm OL,J} = 0.6$$

$$\bullet V_{\rm IL,J} = 2.5$$

$$\bullet V_{\rm IH,J} = 3$$

•

$$V_{OH,J} = 4.5$$

•

$$V_{OL,K} = ???$$

•

$$V_{IL.K} = ???$$

$$\bullet \quad V_{IH,K} = ???$$

•

$$V_{OH,K} = ???$$

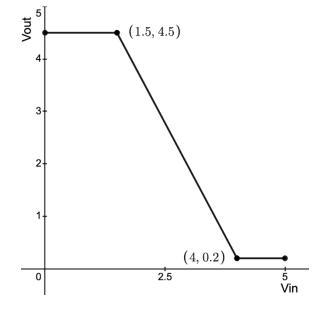

You combine J and K into one functioning device, which you call L.

(D) (2 points) First let's check that device **K** accepts the outputs from **J**. Provide expressions for the constraints on V<sub>IL,K</sub> and V<sub>IH,K</sub> in terms of the voltage thresholds of **J** to ensure that outputs of **J** will be valid inputs to **K**. Also provide an expression for the noise immunity of the connection between **J** and **K**.

Constraint on  $V_{IL,K}$  in terms of J thresholds:  $V_{IL,K} > V_{OL,J} = 0.6$

Constraint on  $V_{IH,K}$  in terms of J thresholds: \_\_\_\_\_  $V_{IH,K} < V_{OH,J} = 4.5$ \_\_\_\_\_

Noise Immunity of connection between J and K: \_\_\_\_\_ min(V<sub>II,K</sub> - 0.6, 4.5 - V<sub>IH,K</sub>)\_\_\_\_\_

(E) (3 points) Now provide an expression for the voltage thresholds and noise immunity of the device  $\mathbf{L}$  in terms of  $V_{OL,K}$ ,  $V_{IL,K}$ ,  $V_{IH,K}$ , and  $V_{OH,K}$  and the J thresholds given above. You may assume that the noise immunity of the wire between  $\mathbf{J}$  and  $\mathbf{K}$  is large enough that it won't affect the voltage thresholds or noise immunity of  $\mathbf{L}$ .

V<sub>OL,L</sub>: \_\_\_\_V<sub>OL,K</sub>\_\_\_ V<sub>IL,L</sub>: \_\_\_2.5\_\_ V<sub>IH,L</sub>: \_\_\_3\_\_ V<sub>OH,K</sub>\_\_\_

Noise Immunity of L: \_\_\_\_\_ min(2.5 - V<sub>OL,K</sub>, V<sub>OH,K</sub> - 3)\_\_\_\_

(F) (2 points) We've finally found the voltage thresholds for device K.

- $\bullet \quad V_{OL,K} = 0.2 V_{DD}$

- $V_{IL,K} = 2$

- $V_{IH,K} = 3.1$

- $V_{OH,K} = 0.8V_{DD}$

Given these constraints, find the value of V<sub>DD</sub> that maximizes the noise immunity of L.

To maximize the noise immunity you want to set the low noise margin equal to the high noise margin. So  $2.5 - V_{OL,K} = V_{OH,K} - 3$ . Substituting in the values of  $V_{OL,K}$  and  $V_{OH,K}$ , we get:  $2.5 - 0.2V_{DD} = 0.8V_{DD}$  -3

$V_{DD} = 5.5V$

| $V_{DD}$ : | 5.5 |  |

|------------|-----|--|

## Problem 2. Boolean Algebra (18 points)

(A) (4 points) Matthew has been given the task of implementing a Boolean function for Queen Frog's annual census of her domain. The function F takes in three Boolean variables, x, y, z and returns:

$$F(x, y, z) = \overline{xy + z} + \overline{yz + x} + xy\overline{z}$$

Fill in the truth table below. Then find the normal form and a minimal sum-of-products expression for F(x, y, z).

| x | у | Z | F |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

1. Normal form for  $F = x\bar{y}\bar{z} + x\bar{y}z + x\bar{y}\bar{z} + x\bar{y}\bar{z$

$$= (\bar{x}\bar{y} + \bar{x}y + x\bar{y} + xy)\bar{z} + \bar{x}\bar{y}z$$

$$=(\bar{x}+x)\bar{z}+\bar{x}\bar{y}z$$

$$= \bar{z} + \bar{x}\bar{y}z$$

$$= \bar{z} + \bar{x}\bar{y}\bar{z} + \bar{x}\bar{y}z = \bar{z} + \bar{x}\bar{y}$$

2. Minimal sum of products for  $F = \underline{z} + \bar{x}\bar{y}$

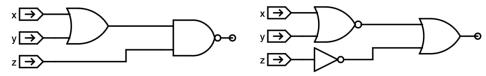

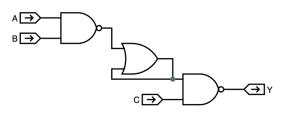

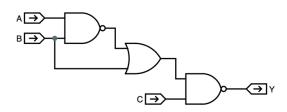

(B) (3 points) Draw the circuit that implements F using 3 or fewer gates. You may only use inverters and 2-input OR, NOR, AND, and NAND gates in your circuit.

(C) (3 points) Queen Frog is delighted with Matthew and appoints him Head of the Census. She then asks him to construct all possible Boolean functions using only *F* gates and constants, which are the only gates she has available. Determine whether *F* is universal or not. Explain your answer. (*F* is included again below for your convenience.)

$$F(x,y,z) = \overline{xy+z} + \overline{yz+x} + xy\overline{z}$$

**Yes.** F(x, y, 1) is NOR, which is universal, and F(0, x, y) is NAND which is also universal.

(D) (8 points) Matthew performs so well that Queen Frog assigns him even more Boolean expressions to simplify! Help Matthew by **finding a minimal sum-of-products** expression for each of the following Boolean expressions. Make sure your answer is in minimal-sum-of products form.

1.

$$a + \overline{(\bar{a} + \bar{b})(c + b)}$$

=  $a + \overline{(\bar{a} + \bar{b})} + \overline{(c + b)}$  (De Morgan's Law)

=  $a + ab + \bar{b}\bar{c}$  (De Morgan's Law)

=  $a + \bar{b}\bar{c}$  (Absorption)

2.

$$b(\bar{a}+c) + a(\bar{c}+b)(c+b)$$

=  $\bar{a}b + bc + a(b)$  (Reduction on AND)

=  $b + \bar{b}\bar{c}$  (Reduction on OR)

=  $b$  (Absorption)

3.

$$a + b\bar{a} + c + \bar{a}\bar{b}\bar{c}$$

$$= a + ab + b\bar{a} + c + \bar{a}\bar{b}\bar{c} \qquad \text{(Reverse absorption)}$$

$$= a + b + c + \bar{a}\bar{b}\bar{c} \qquad \text{(Reduction)}$$

$$= a + a\bar{b}\bar{c} + b + b\bar{c} + c + \bar{a}\bar{b}\bar{c} \qquad \text{(Reverse absorption)}$$

$$= a + \bar{b}\bar{c} + b + b\bar{c} + c \qquad \text{(Reduction)}$$

$$= a + b + \bar{c} + c \qquad \text{(Reduction)}$$

$$= a + b + 1 \qquad \text{(Reduction)}$$

$$= 1 \qquad \text{(Identity)}$$

← alt.: we can observe here a + b + c means "any 1s" and  $\bar{a}\bar{b}\bar{c}$  means "no 1s." this partitions the space of possibilities, and we are done.

4.

$$(a + \overline{bc})(a + \overline{\overline{b} + \overline{c}}) + abc$$

**Solution 1**: Note that  $\overline{bc} = \overline{b} + \overline{c}$ . Thus, it is of the form  $(a + x)(a + \overline{x}) + abc = a + abc = a$ . **Solution 2**:  $(a + \overline{bc})(a + \overline{b} + \overline{c}) + abc = aa + a\overline{bc} + a\overline{b} + \overline{c} + \overline{bc} \cdot \overline{b} + \overline{c} + abc = a + \overline{bc} \cdot \overline{b} + \overline{c} = a + \overline{bc} \cdot (bc) = a + 0 = a$ .

#### **Problem 3. CMOS Logic (16 points)**

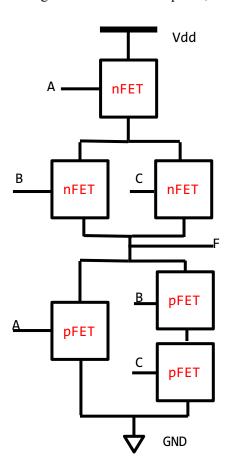

Ben was scrolling on TikTok instead of paying attention to the CMOS lecture, so when he implemented his CMOS circuit below, the VTC he got *for some input values* is the one shown in Figure 1. It doesn't look right to him, but he can't quite figure out what's wrong with it either.

Figure 1: The initial VTC of Ben's circuit.

(A) (2 points) Help Ben figure out what's wrong with his circuit by labeling each blank box of his CMOS diagram as an nFET or a pFET, such that they correspond to the VTC he is getting.

(B) (3 points) Why does the VTC curve look like that? *Hint: note that valid inputs are leading to invalid outputs.*

nFETs are not able to drive the output all the way to Vdd because once the source goes above Vdd-Vth the nFET will turn off. Similarly, pFETs cannot drive the output all the way to GND because once the source goes below Vth the pFET will turn off.

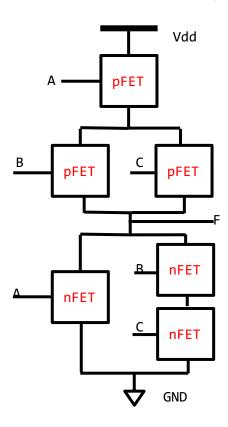

(C) (5 points) Now design a correct CMOS diagram that implements the function above, but does not have the issues Ben experienced with his design, i.e., valid and stable inputs should lead to valid and stable outputs. Once again, label each box as an nFET or pFET. Then, provide a Boolean expression for this function F in terms of A, B, and C.

Boolean expression for F(A, B, C): A + BC

(D) (3 points) What does the new VTC curve look like for the same inputs as the one shown in Figure 1? (approximate shape is ok)

(E) (3 points) **Ben has now invented a new CMOS gate G** that implements a function described by the truth table below. However, he once again became distracted with TikTok and didn't notice that he copied the truth table for his gate G (Figure 2) incorrectly. He does, however, know that he has put an extra 1 where a 0 should have been.

Please correct the truth table by replacing the appropriate 1 with a 0 and explain why it was incorrect.

| A | В | C | G |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

Figure 2: Truth table for Ben's circuit.

### **Explanation:**

We are told that one of the 1's in column G is wrong. It can't be the first row because all CMOS gates must produce a 1 when the inputs are all 0. So we need to consider rows 3 (G(0,1,0)) and 7 (G(1,1,0)). If exactly one of them is wrong, it must be row 7 because if row 3 produced a 0 then we would have a case of a falling input of A causing a falling output which is not possible in CMOS. So the output for G(1,1,0) should be 0.

### **Problem 4. Combinational Circuits (15 points)**

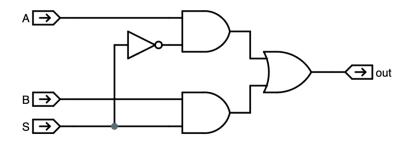

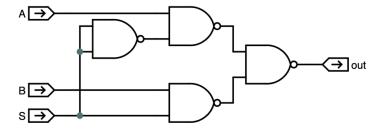

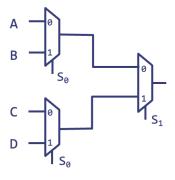

A 1-bit 2-to-1 mux takes in inputs A, B, S and outputs A if S is 0, and B if S is 1.

out =

$$A \cdot \overline{S} + B \cdot S$$

(A) (1 point) Draw a circuit that implements a 2-to-1 1-bit mux using only inverters and 2-input OR and AND gates. Make sure to clearly label all inputs and outputs.

(B) (2 points) Draw a circuit that implements a 2-to-1 1-bit mux using only 2-input NAND gates. Make sure to clearly label all inputs and outputs. For full credit, use **no more than 4 gates**. *Hint: how could you build an INV with only a single NAND gate?*

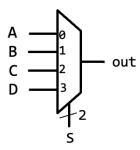

Similarly, we can also build N-to-1 muxes, which take in N inputs, and a log<sub>2</sub>(N)-bit selector. Below is an example of a 4-to-1 mux.

| S[1] | S[0] | out |

|------|------|-----|

| 0    | 0    | A   |

| 0    | 1    | В   |

| 1    | 0    | С   |

| 1    | 1    | D   |

(C) (2 points) Write a minimal sum of products expression for the output out of a 1-bit 4-to-1 mux based on the inputs A, B, C, D, S[1], and S[0].

## Minimal sum of products for out =

$$A\overline{S[1]}\overline{S[0]} + B\overline{S[1]}S[0] + CS[1]\overline{S[0]} + DS[1]S[0]$$

(D) (2 points) Draw a circuit that implements a 4-to-1 mux using only 2-to-1 muxes. Make sure to clearly label all inputs and outputs as well as the select value corresponding to each input.

(E) (8 points) Write a parametric function that implements a 1-bit N-to-1 mux using recursion, where N is a power of 2 (and  $N \ge 2$ ). You may represent the N 1-bit inputs as a single N-bit input in. This effectively is an  $n^{th}$  bit selector. The base case function has been provided for you.

```

function Bit#(1) mux#(2)(Bit#(2) in, Bit#(1) sel);

return (sel == 0) ? in[0]:in[1];

endfunction

function Bit#(1) mux#(Integer n)(Bit#(n) in, Bit#(log2(n)) sel);

Bit#(1) upper = mux#(n/2)(in[n-1:n/2], sel[log2(n)-2:0]);

Bit#(1) lower = mux#(n/2)(in[n/2-1:0], sel[log2(n)-2:0]);

return mux#(2)({upper, lower}, sel[log2(n)-1]);

```

endfunction

6.191 Fall 2023 - 14 of 19 - Quiz #1 Solutions

## **Problem 5. Sequential Circuit Timing (18 points)**

(A) (4 points) For each of the following circuits, determine if it is a valid combinational circuit and if so provide its propagation and contamination delays, otherwise label it as invalid. Assume that each gate has a  $t_{cd}$  of 1 ns and a  $t_{pd}$  of 2 ns.

i.

t<sub>cd</sub> (ns) or Invalid: \_\_\_Invalid\_\_\_

tpd (ns) or Invalid: \_\_\_Invalid\_\_\_

ii.

t<sub>cd</sub> (ns) or Invalid: \_\_\_\_1

t<sub>pd</sub> (ns) or Invalid: \_\_\_\_\_6\_\_\_

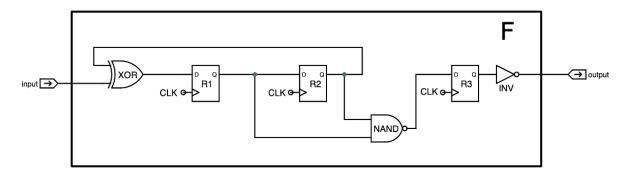

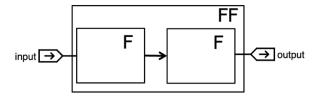

Next, consider the following sequential circuit, F, with the timing constraints specified in the table below.

| Component | t <sub>pd</sub> (ns) | t <sub>cd</sub> (ns) | t <sub>hold</sub> (ns) | t <sub>setup</sub> (ns) |

|-----------|----------------------|----------------------|------------------------|-------------------------|

| R1        | 1                    | 0.5                  | 0                      | 1                       |

| R2        | 2                    | 1                    | ?                      | 1.5                     |

| R3        | 3                    | 2                    | ?                      | 2                       |

| XOR       | 5                    | 1                    |                        |                         |

| NAND      | 2                    | 1.5                  |                        |                         |

| INV       | 1                    | 0.5                  |                        |                         |

(B) (4 points) Provide maximum values for  $t_{hold}$  for registers R2 and R3 that will make this circuit operate as a valid sequential circuit.

$t_{hold,R2}$  is constrained by  $t_{cd,R1} = 0.5$

$t_{hold,R3}$  is constrained by  $t_{cd,R1}+\ t_{cd,NAND}=0.5+1.5=2$

(C) (3 points) Assuming valid values for t<sub>hold,R2</sub> and t<sub>hold,R3</sub>, specify the minimum clock period for this circuit. Show your work.

$$R1 - R2$$

:  $t_{pd,R1} + t_{setup,R2} = 1 + 1.5 = 2.5$

$$R2 - R1$$

:  $t_{pd,R2} + t_{pd,XOR} + t_{setup,R1} = 2 + 5 + 1 = 8$

$$R1 - R3$$

:  $t_{pd,R1} + t_{pd,NAND} + t_{setup,R3} = 1 + 2 + 2 = 5$

$$R2 - R3$$

:  $t_{pd,R2} + t_{pd,NAND} + t_{setup,R3} = 2 + 2 + 2 = 6$

Longest path is R2-R1 so  $t_{CLK} = 8ns$ .

| $t_{clk,F}$ | (ns): | 8 | <u> </u> |  |  |  |

|-------------|-------|---|----------|--|--|--|

|-------------|-------|---|----------|--|--|--|

(D) (4 points) What are the contamination delay and propagation delay of circuit F?

$$\begin{split} t_{cd,F} &= t_{cd,R3} + \ t_{cd,INV} = 2 + 0.5 = 2.5 \\ t_{pd,F} &= t_{pd,R3} + \ t_{pd,INV} = 3 + 1 = 4 \end{split}$$

- t<sub>cd,F</sub> (ns): \_\_\_\_\_2.5\_\_\_\_

- t<sub>pd,F</sub> (ns): \_\_\_\_4\_\_\_

(E) (3 points) You now, want to connect two F components back to back as shown below so that the output of the first F module becomes the input to the second F module. What are the clock period, contamination delay, and propagation delay of this combined circuit, FF? Show your work.

Contamination and propagation delay remain the same for FF as for F. They are calculated from the last register to the output.

For  $t_{\text{CLK}}$ , we now have one additional path to consider from R3 to R1.

R3 - R1:  $t_{pd,R3} + t_{pd,INV} + t_{pd,XOR} + t_{setup,R1} = 3 + 1 + 5 + 1 = 10$ . This is now the longest path so it determines  $t_{CLK}$ .

- t<sub>clk,FF</sub> (ns): \_\_\_\_\_10\_\_\_\_

- t<sub>cd,FF</sub> (ns): \_\_\_\_\_2.5\_\_\_\_

- t<sub>pd,FF</sub> (ns): \_\_\_\_\_4\_\_\_

#### **Problem 6. Seasons Finite State Machine (15 points)**

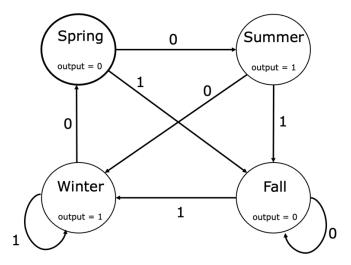

Consider the following finite state machine. The initial state is Spring.

(A) (3 points) Complete the truth table for this FSM below.

| <b>Current State</b> | input | Next State | output |

|----------------------|-------|------------|--------|

| Spring               | 0     | Summer     | 0      |

| Spring               | 1     | Fall       | 0      |

| Summer               | 0     | Winter     | 1      |

| Summer               | 1     | Fall       | 1      |

| Fall                 | 0     | Fall       | 0      |

| Fall                 | 1     | Winter     | 0      |

| Winter               | 0     | Spring     | 1      |

| Winter               | 1     | Winter     | 1      |

(B) (1 point) How many flip flops are needed to implement this FSM?

| Number of flip flops: 2 |  |

|-------------------------|--|

|-------------------------|--|

(C) (3 points) Given the following inputs, determine the next state after the entire input has been processed. Assume that our FSM starts at the initial state for all inputs. Assume that the inputs are processed from left to right.

i. 10000001 Next State: \_\_\_\_**Winter**\_\_\_\_

ii. 010111111000 Next State: \_\_\_\_**Winter**\_\_\_\_

iii. 010000001100011111111111 Next State: \_\_\_\_Winter\_\_\_\_

(D) (4 points) For the following input sequence, determine the current state, next state, and output for each cycle. Assume we start at the initial state, Spring, in cycle 1.

| Cycle            | 1      | 2    | 3    | 4      | 5      | 6      | 7      | 8      |

|------------------|--------|------|------|--------|--------|--------|--------|--------|

| Current<br>State | Spring | Fall | Fall | Fall   | Winter | Winter | Winter | Winter |

| Input            | 1      | 0    | 0    | 1      | 1      | 1      | 1      | 0      |

| Next<br>State    | Fall   | Fall | Fall | Winter | Winter | Winter | Winter | Spring |

| Output           | 0      | 0    | 0    | 0      | 1      | 1      | 1      | 1      |

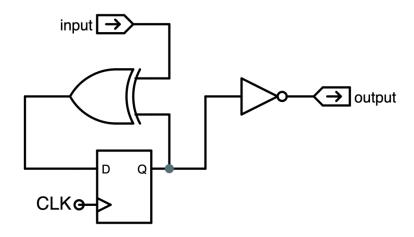

(E) (4 points) Consider a new FSM with the following truth table. Complete the circuit below to implement this FSM.

| Current | input | Next  | output |

|---------|-------|-------|--------|

| State   |       | State |        |

| 0       | 0     | 0     | 1      |

| 0       | 1     | 1     | 1      |

| 1       | 0     | 1     | 0      |

| 1       | 1     | 0     | 0      |

# **END OF QUIZ 1!**