| 1 | /18 |

|---|-----|

| 2 | /18 |

| 3 | /15 |

| 4 | /15 |

| 5 | /16 |

| 6 | /18 |

# MASSACHUSETTS INSTITUTE OF TECHNOLOGY DEPARTMENT OF ELECTRICAL ENGINEERING AND COMPUTER SCIENCE

# **6.191 Computation Structures** Fall 2024

### Quiz #1

| Name                     |                 | Athena logi | n name   | Score              |

|--------------------------|-----------------|-------------|----------|--------------------|

|                          |                 |             |          |                    |

| Recitation section       |                 |             |          |                    |

| ☐ WF 10, 34-301 (Varun)  | □ WF 2, 34-303  | (Pleng)     | □ WF 12  | 2, 34-303 (Ezra)   |

| ☐ WF 11, 34-301 (Varun)  | □ WF 3, 34-303  | (Pleng)     | □ WF 1.  | , 34-303 (Ezra)    |

| ☐ WF 12, 34-302 (Keshav) | □ WF 10, 34-302 | (Hilary)    | □ WF 2   | , 34-302 (Jessica) |

| ☐ WF 1, 34-302 (Keshav)  | □ WF 11, 34-302 | (Hilary)    | □ WF 3.  | , 34-302 (Jessica) |

|                          |                 | •           | □ opt-oi | ıt                 |

Please enter your name, Athena login name, and recitation section above. Enter your answers in the spaces provided below. Show your work for potential partial credit. You can use the extra white space and the back of each page for scratch work.

#### **Problem 1. Digital Abstraction (18 points)**

Ben Bitdiddle is trying to build a digital buffer by chaining two digital inverters together. He happens to have two inverter chips, each from a different logic family.

One of the inverter chips is the **74LS04** in the TTL family. It only supports a supply voltage of 5V and has the following specifications:

Guaranteed low output voltage (V<sub>OL</sub>): ≤0.2V

Accepted low input voltage (V<sub>IL</sub>): ≤0.8V

Accepted high input voltage (V<sub>IH</sub>): ≥2V

Guaranteed high output voltage (V<sub>OH</sub>): ≥3.4V

The other chip is **74HC04** in the CMOS family. The chip has the following specifications where  $V_{DD}$  is the supply voltage:

• Guaranteed low output voltage ( $V_{OL}$ ):  $\leq 3\%$  of  $V_{DD}$ • Accepted low input voltage ( $V_{IL}$ ):  $\leq 30\%$  of  $V_{DD}$ • Accepted high input voltage ( $V_{IH}$ ):  $\geq 70\%$  of  $V_{DD}$ • Guaranteed high output voltage ( $V_{OH}$ ):  $\geq 97\%$  of  $V_{DD}$

Ben decided to use two separate power supplies for his two chips. One power supply is used to provide 5V to the 74LS04. Another power supply can be configured to any value for the 74HC04 chip.

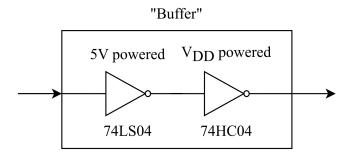

Suppose Ben implements his buffer as in the following diagram:

(A) (2 points) If Ben chooses a supply voltage of  $V_{DD} = 5V$  for the CMOS chip (74HC04), the specifications for the CMOS chip become:  $V_{OL} = 0.15 \text{ V}$ ,  $V_{IL} = 1.5 \text{ V}$ ,  $V_{IH} = 3.5 \text{ V}$ ,  $V_{OH} = 4.85 \text{ V}$ . With this supply voltage, Ben's circuit does not correctly function as a buffer. Explain why the buffer does not work with this supply voltage. Provide a concrete example in your explanation.

## **Explanation:**

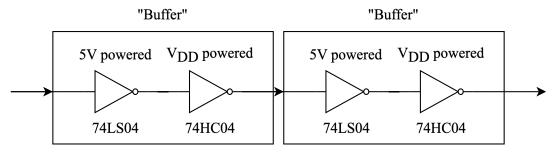

(B) (3 points) Next, Ben decides to try using a supply voltage of  $V_{DD} = 2V$  for the CMOS chip (74HC04). The specifications for the CMOS chip become:  $V_{OL} = 0.06 \text{ V}$ ,  $V_{IL} = 0.6 \text{ V}$ ,  $V_{IH} = 1.4 \text{ V}$ ,  $V_{OH} = 1.94 \text{ V}$ . With this supply voltage, Ben's buffer seems to work correctly, but only in isolation. Ben performs an additional testing of his buffer by connecting two of them in series as in the following diagram:

He expects the overall circuit to still function as a buffer but finds that it does not work as expected. Explain why this supply voltage is also not acceptable.

#### **Explanation:**

(C) (4 points) If Ben chooses a supply voltage of  $V_{DD} = 4.5$ V for the CMOS chip (74HC04), the specifications for the CMOS chip become:  $V_{OL} = 0.135$  V,  $V_{IL} = 1.35$  V,  $V_{IH} = 3.15$  V,  $V_{OH} = 4.365$  V. It is possible to choose a signaling level specification that makes Ben's circuit a legitimate buffer that can be used in isolation or in combination with other circuits. Choose a signaling level specification for Ben's buffer. You should maximize the noise margins.

Be careful about the ordering of variables here.

$V_{OL}$ : \_\_\_\_\_V

$V_{IL}$ : \_\_\_\_\_ V

$V_{IH}$ : \_\_\_\_\_V

$V_{OH}$ : \_\_\_\_\_V

(D) (3 points) What are the conditions on  $V_{DD}$  that must be satisfied to ensure that Ben's circuit functions correctly as a buffer with non-negative noise margins? Make sure to list <u>all</u> the required conditions. Do not forget the constraints you discovered in Part (B). You may leave your answers in un-simplified form.

6.191 Fall 2024 - 4 of 21 - Quiz #1

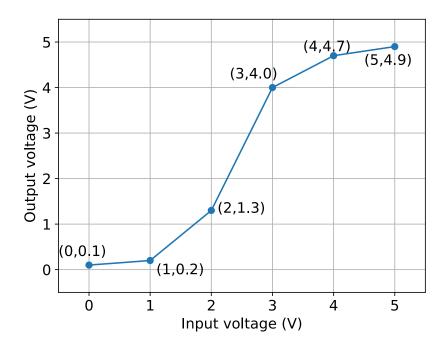

Ben finally realized that building a buffer by chaining two inverters from unrelated logic families is a horrible idea. He decided to scrap the idea and build his own buffer from scratch. He managed to obtain a Voltage Transfer Curve (VTC) for his buffer as in the following plot.

(E) (6 points) For each of the signaling level specifications below, find the noise immunity or write ILLEGAL if the specification is illegal. If the specification is illegal, explain why it is illegal.

Be careful about the ordering of variables here.

Case 1:

$$V_{OL} = 1V$$

,  $V_{IL} = 0.6V$ ,  $V_{IH} = 3V$ ,  $V_{OH} = 4V$

Noise immunity (V) or ILLEGAL:

**Explanation if ILLEGAL:**

Case 2:

$$V_{OL} = 1V$$

,  $V_{IL} = 1.4V$ ,  $V_{IH} = 2.2V$ ,  $V_{OH} = 3.2V$

Noise immunity (V) or ILLEGAL:

**Explanation if ILLEGAL:**

Case 3:

$$V_{OL} = 1V$$

,  $V_{IL} = 1.2V$ ,  $V_{IH} = 3V$ ,  $V_{OH} = 4V$

Noise immunity (V) or ILLEGAL:

**Explanation if ILLEGAL:**

# Problem 2. Boolean Algebra (18 points)

(A) (3 points) Consider the truth table below for the Boolean function F. Find the normal form and a minimal sum-of-products expression for F(A, B, C).

| Α | В | С | F |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

1. What is the normal form expression for F(A, B, C)?

2. What is the minimal sum-of-products expression for F(A, B, C)?

| Minimal sum-of-products form for F = |  |

|--------------------------------------|--|

|--------------------------------------|--|

(B) (3 points) Draw the circuit that implements F using 3 or fewer gates. You may only use inverters and 2-input OR, NOR, AND, and NAND gates in your circuit.

Quiz #1

(C) (2 points) Determine whether the 3-input Boolean function  $G(A, B, C) = AB\overline{C} + C$  is functionally complete (universal). If it is, prove it. Otherwise, explain why it is not.

- (D) (6 points) Find a minimal sum-of-products expression for each of the following Boolean expressions. Pay close attention to which variables are under the overbars. To get credit for your answer, you must use boolean algebra axioms and properties and show your work!

- 1.  $a(b\overline{c} + a) + \overline{ac}$

2.  $\overline{a}bc + bc\overline{d}e + abc\overline{d}$

3.  $\overline{ab(\overline{c}+a)+\overline{bc}+d}$

(E) (4 points) Determine whether each of the Boolean expressions below are satisfiable. If it is satisfiable, give the input assignments that make the expression satisfiable. If it is not satisfiable, show why it is not.

1.

$$(a+b)a\overline{b}(d+cd)$$

2.

$$(a\overline{e} + c)(\overline{ab}c + ad)(\overline{ca})$$

# Problem 3. CMOS Logic (15 points)

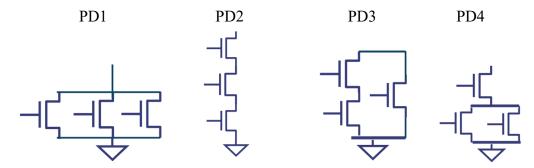

(A)(5 points) You are given several **pulldown** circuits for 3-input CMOS gates. You can choose between the following 4 options

You can connect one of the inputs (A, B, C, D) or a constant (GND, or VDD) to each nFET in the pulldown circuits shown above. Assume that there is a complementary pullup circuit connected to each pulldown. For each of the following Boolean functions, determine whether it can be implemented as one of the given CMOS gates. This could require simplifying the logic equations. If none of the pulldowns can be used to represent the function, write "NONE." If multiple CMOS gates are usable please feel free to choose any of them.

1.

$$F(A, B, C) = \overline{AB + C}$$

2.

$$F(A, B, C, D) = \overline{A} \overline{B} \overline{C} \overline{D} + \overline{A} \overline{B} \overline{C} D$$

3.

$$F(A,B,C) = \overline{CA} + (\overline{BA} + BC)B$$

4.

$$F(A,B,C,D) = \overline{(AB)\overline{(C+D)} + \overline{D+AC}}$$

5.

$$F(A,B,C,D) = (\bar{B} + \bar{C}D)\bar{C} + \overline{DA}$$

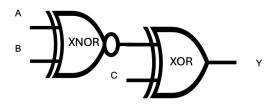

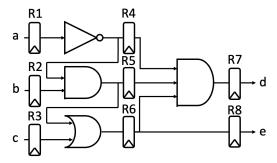

(B) (4 points) For the combinational logic below, determine if it can be implemented with a single CMOS gate. If so, draw the gate using the **minimum number of transistors**. If not explain why this cannot be implemented as a single CMOS gate.

CMOS gate or explanation:

(C) (6 points) For the truth table below, determine if it can be implemented with a single CMOS gate. If so, draw the gate using the **minimum number of transistors**. If not explain why this cannot be implemented as a single CMOS gate.

| A | В | C | Y |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 |

**CMOS** gate or explanation:

#### **Problem 4: Combinational Circuits in Minispec (15 points)**

The company Ben Bitdiddle works at, *John Street*, performs a lot of comparisons between very large dollar amounts stored as integers. Until now, their code made use of chained comparators to perform the computations. To speed things up, Ben decides to convert the chained comparator implementation to a recursively called function to reduce propagation delay.

Ben first thinks of splitting the long chain of bitwise compare operations into upper and lower halves recursively. The rec\_cmp function compares two n-bit values, a and b, and returns a 2-bit output equal to:

- '2b10 if a and b are equal (eq=1),

- '2b01 if a < b (lt=1),

- $^{\circ}$ 2b00 if a > b.

Ben's recursive implementation is shown below.

endfunction

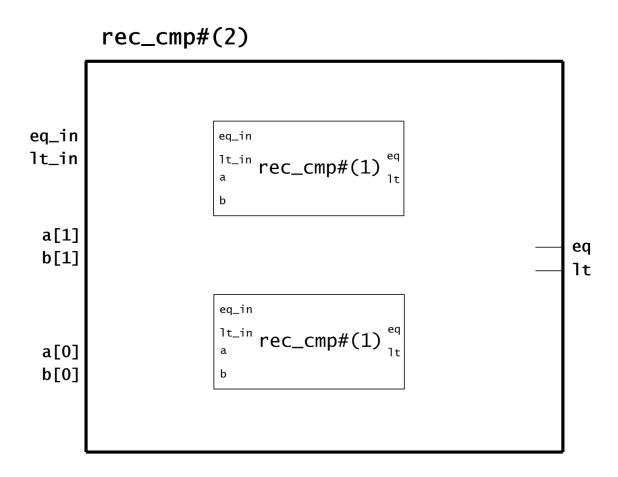

(A) (4 points) Complete the circuit diagram for the above parametric function when n = 2. Blocks representing function calls at n = 1 have been provided. You can also use the standard gates, muxes, and constant inputs of 0 and 1 as needed.

Consider the same circuit for a general parameter n. How does the propagation delay of the circuit grow with n? Provide an explanation for why this is the propagation delay for this implementation.

|                | The propagation delay for this circuit in terms of n is $\Theta($ |  |  |

|----------------|-------------------------------------------------------------------|--|--|

| Justification: |                                                                   |  |  |

|                |                                                                   |  |  |

|                |                                                                   |  |  |

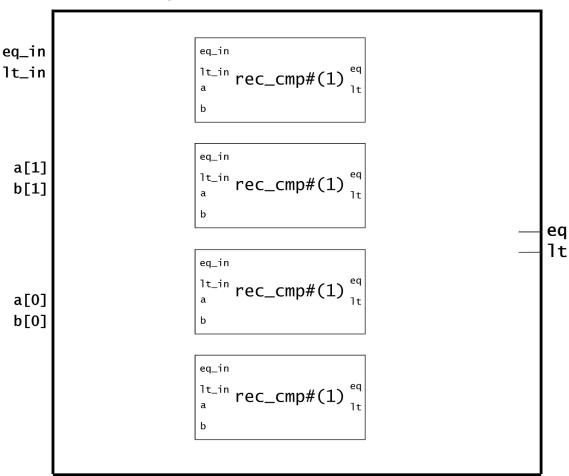

(B) (5 points) After testing his original code on various large numbers, Ben finds that his recursive implementation didn't quite get the speedup he expected. He decides to fix his code to **remove the chaining between the upper and lower** recursive calls. Fix Ben's rec\_cmp function to remove this chaining **between the upper and lower** (Hint: you may need up to 4 recursive calls to rec\_cmp). You may assume that the base case rec\_cmp#(1) is already defined in the same way as in Ben's original code. **Note that n is not necessarily a power of 2.**

endfunction

6.191 Fall 2024 - 13 of 21 - Quiz #1

(C) (6 points) Complete the circuit diagram for the above parametric function when n = 2. Blocks representing function calls at n = 1 have been provided. You can choose to use any number of these blocks, the standard gates, muxes, and constant inputs of 0 and 1 as needed.

# rec\_cmp#(2)

Consider the same circuit for a general parameter n. How does the propagation delay of the circuit grow with n? Provide an explanation for why this is the propagation delay for this implementation.

The propagation delay for this circuit in terms of n is  $\Theta(\underline{\hspace{1cm}})$

| Justification: |  |  |  |

|----------------|--|--|--|

|                |  |  |  |

|                |  |  |  |

|                |  |  |  |

### Problem 5. Combinational and Sequential Logic Timing (16 points)

(A) (4 points) When-vidia is a spinoff of a large gaming and AI hardware company that focuses on clocks and other timing devices. As a bright MIT intern there, you have been tasked with figuring out the exact propagation and contamination delays of circuits that they have built.

They use a logic family with the following characteristics for their circuits (in *nanoseconds*):

| Gate | $t_{PD}$ | $t_{CD}$ |

|------|----------|----------|

| AND2 | 1.7      | 0.4      |

| OR2  | 1.8      | 0.4      |

| NOT  | 0.7      | 0.3      |

| AND3 | 2.4      | 0.6      |

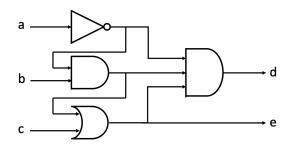

The first circuit they ever designed was purely combinational and looked as follows:

What are the overall  $t_{PD}$  and  $t_{CD}$  values of this circuit?

| t <sub>PD</sub> (ns): |  |

|-----------------------|--|

| t <sub>CD</sub> (ns): |  |

They are now moving on to connecting their combinational logic through some sequential logic elements.

They need to select which type of register to use for their design. They are considering three choices, Reg A, Reg B, and Reg C with timing characteristics shown in the table below. For convenience, we also include a copy of the combinational timing specifications table from the previous page.

| Gate  | t <sub>PD</sub> | tcd | tsetup | $t_{ m Hold}$ |

|-------|-----------------|-----|--------|---------------|

| Reg A | 0.5             | 0.2 | 0.3    | 0.4           |

| Reg B | 0.4             | 0.1 | 0.4    | 0.2           |

| Reg C | 0.6             | 0.4 | 0.3    | 0.3           |

| Gate | t <sub>PD</sub> | t <sub>CD</sub> |

|------|-----------------|-----------------|

| AND2 | 1.7             | 0.4             |

| OR2  | 1.8             | 0.4             |

| NOT  | 0.7             | 0.3             |

| AND3 | 2.4             | 0.6             |

(B) (4 points) If their goal is to produce a **valid** sequential circuit with minimum  $\mathbf{t}_{CLK}$  which type of register should they use? Circle which register type to select and explain why you should choose that register type.

Circle one: Reg A Reg B Reg C

# **Explanation:**

(C) (4 points) Using the register type you selected in part B, please find the minimum  $\mathbf{t}_{CLK}$  value for which this circuit operates correctly. For full credit, you must show that all timing constraints are fully satisfied.

Minimum t<sub>CLK</sub> (ns):

| (D) (4 points) what are the tpb and tcb values of the sequential circu | iit?                  |  |

|------------------------------------------------------------------------|-----------------------|--|

|                                                                        |                       |  |

|                                                                        |                       |  |

|                                                                        |                       |  |

|                                                                        |                       |  |

|                                                                        |                       |  |

|                                                                        | t <sub>PD</sub> (ns): |  |

|                                                                        |                       |  |

|                                                                        | t <sub>CD</sub> (ns): |  |

|                                                                        |                       |  |

### **Problem 6. Finite State Machines (18 points)**

Carrie Ripple is an engineer and just had a baby. She's trying to learn how to get the baby to stop crying, so she has made an FSM to understand the baby's behavior. The baby can be in one of three states:

- Fed (F)

- Cleaned (C)

- Slept (S)

- (A) (2 points) The baby does not speak yet, and for now assume it only has one input signal: crying (r). If the baby is fed and cries, she tries cleaning it. If the baby still cries, she tries getting it to sleep. If it still cries, she tries feeding it again. If in any state the baby stops crying, she does nothing and walks away quietly.

Draw the 3-state FSM for the baby.

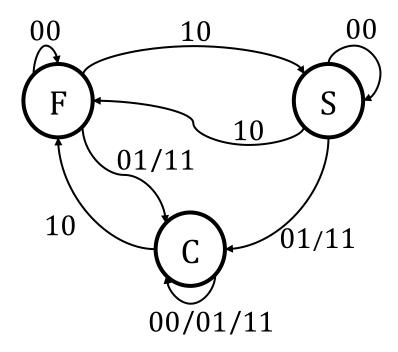

(B) (3 points) Carrie realized that crying is not a sufficient signal to debug the baby. She now also uses the baby smelling sub-optimally (m) to decide what to try next. Below we give you the new FSM for the baby. The input signals are specified using 2-bits where the most significant bit is r (crying) and the least significant bit is m (smelling). If multiple input signals result in the same state transition, they are indicated with a separating / between them.

# Input signals: rm

If the baby is in the Slept state (S) and it cries but doesn't smell, what state does this FSM go to?

| Next State:                                                                            |

|----------------------------------------------------------------------------------------|

| f the baby is in the Cleaned state (C) and it smells, what state does the FSM go to?   |

| Next State:                                                                            |

| Iow many flip flops does the baby debugging FSM require to encode all possible states? |

Number of Flip Flops: \_\_\_\_\_

(C) (3 points) Before Carrie starts using the FSM, she wants to know how the FSM will behave given a series of inputs.

What is the resulting state of the baby at the end of each sequence of inputs provided? Assume the baby is in the Cleaned state (C), at the beginning of each sequence.

| i.   | 10 10 01 00                   | <br> |

|------|-------------------------------|------|

| ii.  | 10 11 01 00 10                |      |

|      |                               | <br> |

| 111. | 11 10 00 11 01 00 01 00 10 10 |      |

(D)(3 points) Fill out the following truth table for Carrie's FSM based on her state transition diagram. The output should be 1 whenever the baby stops crying and stops smelling and it is Fed or Cleaned, and 0 otherwise. Note that although in many FSMs the output only depends on the current state, that is not the case for this FSM.

| State | Input (rm) | Next State | Output |

|-------|------------|------------|--------|

| F     | 00         |            |        |

| F     | 01         |            |        |

| F     | 10         |            |        |

| F     | 11         |            |        |

| S     | 00         |            |        |

| S     | 01         |            |        |

| S     | 10         |            |        |

| S     | 11         |            |        |

| C     | 00         |            |        |

| C     | 01         |            |        |

| С     | 10         |            |        |

| С     | 11         |            |        |

(E) (7 points) Given that the state of this FSM is encoded using 2 bits  $S_1S_0$ , and that the encoding for states F, S, and C are 00, 01, and 10 respectively, implement the baby FSM.

$$In0_m \longrightarrow \bigcirc$$

# **END OF QUIZ 1!**